Strengths can be used to resolve which value should appear on a net or gate output.

A strength specification shall have the following two components:

• The strength of the 0 portion of the net value, called strength0, designated as one of the following:

supply0 strong0 pull0 weak0 highz0

• The strength of the 1 portion of the net value, called strength1, designated as one of the following:

supply1 strong1 pull1 weak1 highz1

The combinations (highz0, highz1) and (highz1, highz0) shall be considered illegal.

There are four driving strengths: supply strong pull weak

Signals with driving strengths shall propagate from gate outputs and continuous assignment outputs.

There are three charge storage strengths: large medium small

Signals with the charge storage strengths shall originate in the trireg net type.

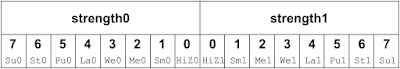

It is possible to think of the strengths of signals as locations on the scale

When signals combine, their strengths and values shall determine the strength and value of the resulting signal in accordance with the principle.

1) If two or more drivers drive a signal with different strength then it will have the value of the strongest driver

Ex-1:

buf (strong1, weak0) g1 (y, a);

buf (pull1, supply0) g2 (y, b);

• If a = 0 and b = 0 then y will be 0 with supply strength because both gates will set y to 0 and supply (7) strength has bigger value than weak (3) strength.

• If a = 0 and b = 1 then y will be 1 with pull strength because g1 will set y to 0 with weak (3) strength and g2 will set y to 1 with pull (5) strength (pull strength is stronger than the weak strength).

• If a = 1 and b = 0 then y will be 0 with supply strength because g1 will set y to 1 with strong (6) strength and g2 will set y to 0 with supply (7) strength (supply strength is stronger than the strong strength).

• If a = 1 and b = 1 then y will be 1 with strong strength because g1 will set y to 1 with strong (6) strength and g2 will set y to 1 with pull (5) strength.

2) The combination of signals identical in strength and value shall result in the same signal (If two drivers of a net have the same strength and value, then the net result will have the same value and strength)

Ex-2:

buf (strong1, weak0) g1 (y, a);

buf (strong1, weak0) g1 (y, b);

• If a = 0 and b = 0 then y will be 0 with weak strength.

• If a = 1 and b = 1 then y will be 1 with strong strength.

3) If two drivers of a net have the same strength but different values then signal value will be unknown and it will have the same strength as both drivers

Ex-3:

buf (strong1, weak0) g1 (y, a);

buf (weak1, strong0) g1 (y, b);

• If a = 1 and b = 0 then y will be x with strong strength.

Important Notes:

If one of the drivers has an H or L value, then the output value will be X.

A strength specification shall have the following two components:

• The strength of the 0 portion of the net value, called strength0, designated as one of the following:

supply0 strong0 pull0 weak0 highz0

• The strength of the 1 portion of the net value, called strength1, designated as one of the following:

supply1 strong1 pull1 weak1 highz1

The combinations (highz0, highz1) and (highz1, highz0) shall be considered illegal.

There are four driving strengths: supply strong pull weak

Signals with driving strengths shall propagate from gate outputs and continuous assignment outputs.

There are three charge storage strengths: large medium small

Signals with the charge storage strengths shall originate in the trireg net type.

It is possible to think of the strengths of signals as locations on the scale

When signals combine, their strengths and values shall determine the strength and value of the resulting signal in accordance with the principle.

1) If two or more drivers drive a signal with different strength then it will have the value of the strongest driver

Ex-1:

buf (strong1, weak0) g1 (y, a);

buf (pull1, supply0) g2 (y, b);

• If a = 0 and b = 0 then y will be 0 with supply strength because both gates will set y to 0 and supply (7) strength has bigger value than weak (3) strength.

• If a = 0 and b = 1 then y will be 1 with pull strength because g1 will set y to 0 with weak (3) strength and g2 will set y to 1 with pull (5) strength (pull strength is stronger than the weak strength).

• If a = 1 and b = 0 then y will be 0 with supply strength because g1 will set y to 1 with strong (6) strength and g2 will set y to 0 with supply (7) strength (supply strength is stronger than the strong strength).

• If a = 1 and b = 1 then y will be 1 with strong strength because g1 will set y to 1 with strong (6) strength and g2 will set y to 1 with pull (5) strength.

2) The combination of signals identical in strength and value shall result in the same signal (If two drivers of a net have the same strength and value, then the net result will have the same value and strength)

Ex-2:

buf (strong1, weak0) g1 (y, a);

buf (strong1, weak0) g1 (y, b);

• If a = 0 and b = 0 then y will be 0 with weak strength.

• If a = 1 and b = 1 then y will be 1 with strong strength.

3) If two drivers of a net have the same strength but different values then signal value will be unknown and it will have the same strength as both drivers

Ex-3:

buf (strong1, weak0) g1 (y, a);

buf (weak1, strong0) g1 (y, b);

• If a = 1 and b = 0 then y will be x with strong strength.

Important Notes:

If one of the drivers has an H or L value, then the output value will be X.

No comments:

Post a Comment